#### Mississippi State University

#### **Scholars Junction**

Theses and Dissertations

Theses and Dissertations

1-1-2005

### Improving Instruction Fetch Rate with Code Pattern Cache for Superscalar Architecture

Azam Muhammad Beg

Follow this and additional works at: https://scholarsjunction.msstate.edu/td

#### **Recommended Citation**

Beg, Azam Muhammad, "Improving Instruction Fetch Rate with Code Pattern Cache for Superscalar Architecture" (2005). *Theses and Dissertations*. 2655.

https://scholarsjunction.msstate.edu/td/2655

This Dissertation - Open Access is brought to you for free and open access by the Theses and Dissertations at Scholars Junction. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholars Junction. For more information, please contact scholcomm@msstate.libanswers.com.

## IMPROVING INSTRUCTION FETCH RATE WITH CODE PATTERN CACHE

FOR SUPERSCALAR ARCHITECTURE

By

Azam Muhammad Beg

A Dissertation

Submitted to the Faculty of

Mississippi State University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in Computer Engineering

in the Department of Electrical and Computer Engineering

Mississippi State, Mississippi

August 2005

Copyright by

Azam Muhammad Beg

2005

# IMPROVING INSTRUCTION FETCH RATE WITH CODE PATTERN CACHE FOR SUPERSCALAR ARCHITECTURE

By

#### Azam Muhammad Beg

Approved:

Yul Chu Assistant Professor of Electrical and Computer Engineering (Director of Dissertation) Justin Davis

Assistant Professor of Electrical

and Computer Engineering

(Committee Member)

Nicolas H. Younan Professor of Electrical and Computer Engineering (Committee Member/Graduate Program Director)

Susan M. Bridges Professor of Computer Science and Engineering (Committee Member)

Kirk H. Schulz Dean of the Bagley College of Engineering

Name: Azam Muhammad Beg

Date of Degree: August 6, 2005

Institution: Mississippi State University

Major Field: Computer Engineering

Major Professor: Dr. Yul Chu

Title of Study: IMPROVING INSTRUCTION FETCH RATE WITH CODE-

PATTERN CACHE FOR SUPERSCALAR ARCHITECTURE.

Pages in Study: 125

Candidate for Degree of Philosophy

In the past, instruction fetch speeds have been improved by using cache schemes that capture the actual program flow. In this dissertation, we present the architecture of a new instruction cache named *code* pattern cache (CPC); the cache is used with superscalar processors.

CPC's operation is based on the fundamental principles that: common programs tend to repeat their execution patterns; and efficient storage of a program flow can enhance the performance of an instruction fetch mechanism. CPC saves basic blocks (sets of instructions separated by control instructions) and their boundary addresses while the code is running. Basic blocks and their addresses are stored in two separate

structures, called *block pointer cache* (BPC) and *basic block cache* (BBC), respectively. Later, if the same basic block sequence is expected to execute, it is fetched from CPC, instead of the instruction cache; this mechanism results in higher likelihood of delivering a larger number of instructions in every clock cycle.

We developed single and multi-threaded simulators for TC, BC, and CPC, and used them with 10 SPECint2000 benchmarks. The simulation results demonstrated CPC's advantage over TC and BC, in terms of *trace miss rate* and *average trace length*. Additionally, we used cache models to quantify the timing, area, and power for the three cache schemes. Using an aggregate performance index that combined the simulation and modeling results, CPC was shown to perform better than both TC and BC.

During our research, each of the TC-, BC-, or CPC-configurations took 4-6 hours to simulate, so performance comparison of these caches proved to be a very time-consuming process. Neural network models (NNM's) can be time-efficient alternatives to simulations, so we studied their feasibility to represent the cache behavior. We developed two NNM's, one to predict the trace miss rate and the other to predict the average trace length for the three caches. The NNM's modeled the caches with reasonable accuracy, and produced results in a fraction of a second.

#### **DEDICATION**

I dedicate this research to my loving parents and wife.

#### **ACKNOWLEDGMENTS**

First and foremost, I thank Allah, the God, the Most Merciful, the Beneficent for blessing me with the countless bounties of abilities and resources in this life.

I feel highly indebted to my advisor Dr. Yul Chu for providing me with constant guidance and supervision and for pushing me, at times to accomplish more than what I would have otherwise settled for. I thank my committee members Drs. Younan, Davis, and Bridges for their insightful commentary on my research. I am thankful to the ECE department for the much needed financial support in the last phase of my research.

I owe my deepest gratitude to my parents for the values they instilled in me while bringing me up and for teaching me the lessons about hard work and persistence.

I would also like to thank my wife Shabana; without her support and patience, it would have not been possible to complete this arduous journey. I appreciate my whole family including my children Raahim and Rahma for letting me busy with my studies during many, many evenings

and nights in the last 8 years, especially during the last few months of my PhD program.

I also value the "Just Do It" words of encouragement, I often received from my friends Drs. Amr and Ashraf.

Finally, I would also like to say a word of appreciation to everyone who helped me with my PhD degree in one way or other.

#### TABLE OF CONTENTS

|      |                                               |                                                                                                                                                                                                                                                                                                                               | Page                                                                    |

|------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| DED! | ICATIC                                        | ON                                                                                                                                                                                                                                                                                                                            | ii                                                                      |

| ACKI | NOWLE                                         | EDGMENTS                                                                                                                                                                                                                                                                                                                      | iii                                                                     |

| LIST | OF TA                                         | BLES                                                                                                                                                                                                                                                                                                                          | viii                                                                    |

| LIST | OF FIC                                        | GURES                                                                                                                                                                                                                                                                                                                         | ix                                                                      |

| CHAI | PTER                                          |                                                                                                                                                                                                                                                                                                                               |                                                                         |

| I.   | INTRO                                         | ODUCTION                                                                                                                                                                                                                                                                                                                      | 1                                                                       |

|      | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6        | Background  1.1.1 Microprocessor Performance  1.1.2 Overview of Thread-Level Parallelism  1.1.3 Basic Blocks  1.1.4 Conventional Instruction Cache. Related Works.  1.2.1 Trace Cache  1.2.2 Block Caches.  1.2.3 Modeling Techniques  Motivation.  Contributions  Performance Evaluation  Organization of this Dissertation. | 3<br>3<br>5<br>11<br>13<br>17<br>17<br>20<br>23<br>26<br>29<br>30<br>32 |

| II.  | CODE                                          | E PATTERN CACHE                                                                                                                                                                                                                                                                                                               | 33                                                                      |

|      | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | CPC Overview  CPC-ST Architecture  2.2.1 Storage Module  2.2.2 Trace Build Engine  2.2.3 Merging Buffer  2.2.4 Branch Predictor  CPC-ST Operation  2.3.1 Trace Assembly Mode                                                                                                                                                  | 33<br>38<br>38<br>42<br>42<br>43<br>44<br>48                            |

| CHA  | PTER | I                                                                                        | Page     |

|------|------|------------------------------------------------------------------------------------------|----------|

|      |      | 2.3.2 Trace Delivery Mode                                                                | 49<br>50 |

|      |      | 2.3.4 Miss Rate Related Cases                                                            | 50       |

|      |      | 2.3.5 Cache Replacement Policy                                                           | 53       |

|      |      | 2.3.5.1 BPC Line Replacement                                                             | 53       |

|      |      | 2.3.5.2 BBC-Way Selection & Replacement                                                  | 54       |

|      | 2.4  | 2.3.6 Cache Structure Indexing  CPC-MT Architecture                                      | 56<br>60 |

|      | 2.5  | CPC-MT Architecture  CPC-MT Operation                                                    | 61       |

| III. | COD  | E PATTERN CACHE SIMULATION & MODELING                                                    | 63       |

|      | 3.1  | CPC Simulation                                                                           | 63       |

|      | 0.1  | 3.1.1 Sim-CPC                                                                            | 63       |

|      |      | 3.1.2 Benchmark Programs                                                                 | 66       |

|      |      | 3.1.3 Workload Mixes                                                                     | 66       |

|      |      | 3.1.4 Simulation Results                                                                 | 67       |

|      |      | 3.1.4.1 Miss Rates in Single-ThreadedEnvironment                                         | 68       |

|      |      | 3.1.4.2 Miss Rates in Multi-Threaded Environment 3.1.4.3 Trace Length in Single-Threaded | 69       |

|      |      | Environment                                                                              | 70       |

|      |      | 3.1.4.4 Trace Length in Multi-Threaded                                                   |          |

|      |      | Environment                                                                              | 71       |

|      |      | 3.1.4.5 CPC's Overall Gains in Trace Miss Rate                                           |          |

|      |      | and Trace Length                                                                         | 72       |

|      |      | 3.1.4.6 Design Space Study                                                               | 73       |

|      | 3.2  | CPC Modeling                                                                             | 78       |

|      |      | 3.2.1 CACTI                                                                              | 78       |

|      |      | 3.2.2 Using CACTI                                                                        | 79       |

|      |      | 3.2.3 Modeling Results                                                                   | 80       |

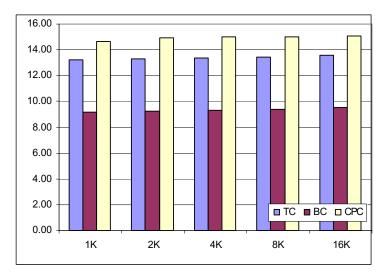

|      |      | 3.2.3.1 Access Time                                                                      | 80       |

|      |      | 3.2.3.2 Consumed Power                                                                   | 81       |

|      |      | 3.2.3.3 Area                                                                             | 83       |

|      | 3.3  | Combining Simulation and Modeling Results                                                | 84       |

| IV.  | NEU  | RAL NETWORK MODELS FOR CACHES                                                            | 86       |

|      | 4.1  | Neural Networks                                                                          | 86       |

|      |      | 4.1.1 Processing Elements                                                                | 86       |

|      |      | 4.1.2 A 3-Layer NN Topology                                                              | 89       |

|      |      | 4.1.3 Learning Mechanism                                                                 | 90       |

|      |      | 4.1.4 Motivation                                                                         | 92       |

|      | 4.2  | Neural Network Modeling for TC, BC, and CPC                                              | 92       |

| CHAPTER  |                                             | Page |

|----------|---------------------------------------------|------|

|          | 4.2.1 Experimental Methodology              | 92   |

|          | 4.2.2 Input-Output Definition               |      |

|          | 4.2.3 Data Pre-Processing                   | 95   |

|          | 4.2.4 Neural Network Training and Testing   |      |

|          | 4.2.5 Experimental Results and Analysis     | 98   |

| 4.3      | Conclusions                                 | 100  |

| V. CONC  | LUSIONS & FUTURE RESEARCH                   | 102  |

| 5.1      | Conclusions                                 | 103  |

| 5.2      | Future Research                             |      |

| 0.2      | 5.2.1 CPC Architecture & Simulations        |      |

|          | 5.2.2 Power, Area, and Access Time Modeling |      |

|          | 5.2.3 Neural Network Modeling               |      |

| APPENDIX |                                             |      |

| SPEC     | INT2000 BENCHMARKS                          | 109  |

| DEFEDENC | ALC C                                       | 110  |

#### LIST OF TABLES

| TABI | LE                                                                                                                                            | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1    | Configuration parameters for Sim-TC, Sim-BC, and Sim-CPC                                                                                      | . 65 |

| 2    | Benchmarks for comparing CPC with TC and BC                                                                                                   | . 66 |

| 3    | Integer workload mixes for single and multi-threaded simulations                                                                              | . 67 |

| 4    | Miss rate comparison for single and multi-threaded environments                                                                               | . 72 |

| 5    | Trace length comparison for single and multi-threaded environments                                                                            | . 73 |

| 6    | CACTI model parameters for TC, BC, and CPC                                                                                                    | . 80 |

| 7    | Aggregate performance index (API) for different cache sizes - CPC vs. TC                                                                      | . 85 |

| 8    | Aggregate performance index (API) for different cache sizes - CPC vs. BC                                                                      | . 85 |

| 9    | Neural Network Configurations - Input and Output Neurons                                                                                      | . 94 |

| 10   | Training performance for trace miss-rate NNM ("Configuration-2"): optimum results were achieved with a 4-layer (6-5-5-1) NNM (shown in bold)* | . 97 |

| 11   | Training performance for trace-length NNM  ("Configuration-4"): optimum results were achieved with a 4-layer (6-15-10-1) NNM (shown in bold)  | . 98 |

#### LIST OF FIGURES

| FIGU | JRE                                                                                                                                                                                                                                                                                          | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

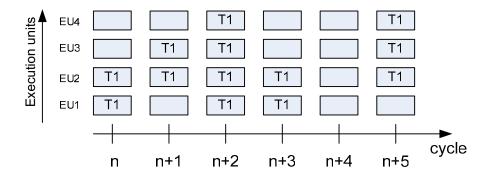

| 1    | States of 4 execution units of a superscalar processor executing a single thread (T1)                                                                                                                                                                                                        | 8    |

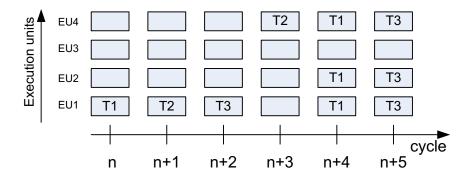

| 2    | States of 4 execution units of a fine-grain MT processor executing 3 threads (T1, T2, T3); threads switch in round-robin fashion every cycle.                                                                                                                                                | 8    |

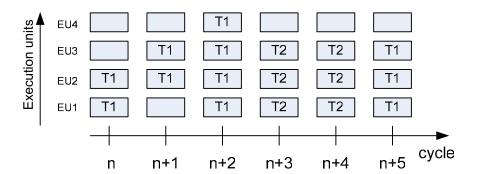

| 3    | States of 4 execution units of coarse-grain MT processor executing two threads (T1 and T2); thread switches from T1 to T2 in cycle n+3 due to long stall on thread T1                                                                                                                        | 9    |

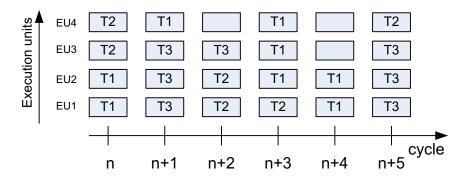

| 4    | States of 4 execution units of a simultaneous multi-threading (SMT) processor; based on the availability of execution units, instructions from one or more threads are allowed to execute every cycle.                                                                                       | 10   |

| 5    | Four basic blocks from a sample program are shown. Block beginnings (heads) and (tails) are also identified. (Addresses are shown in hexadecimal format)                                                                                                                                     |      |

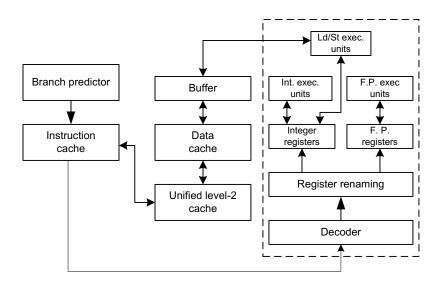

| 6    | A superscalar processor with an instruction cache (IC)                                                                                                                                                                                                                                       | 14   |

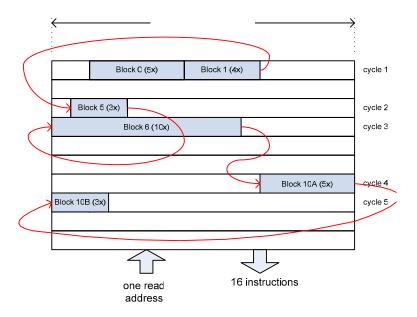

| 7    | Basic blocks in the lines of an IC: 5 cycles are required to fetch the non-contiguous basic blocks due to taken branches. (The arrows show the sequence of instruction execution)                                                                                                            | 15   |

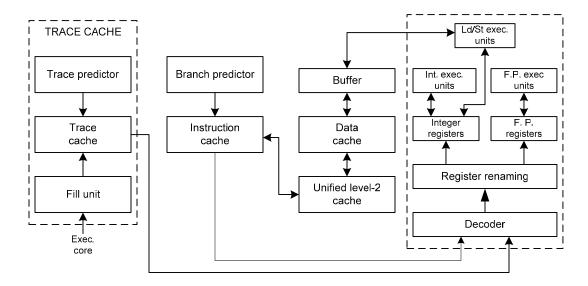

| 8    | A superscalar processor with a trace cache (TC)                                                                                                                                                                                                                                              | 18   |

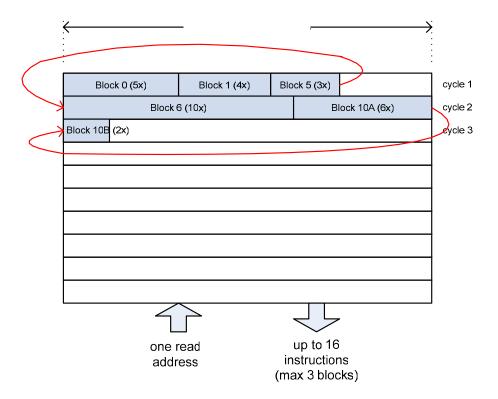

| 9    | Basic blocks in the lines of a trace cache (TC): A maximum of 16 instructions or 3 basic blocks are stored in a TC line. 'Instruction holes' are left at the end of the first cache line. In cycle-1, 3 basic blocks are delivered. (The arrows show the sequence of instruction execution). | 19   |

| FIGU | RE                                                                                                                                                                                                                                                                                                                                                                                     | age |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

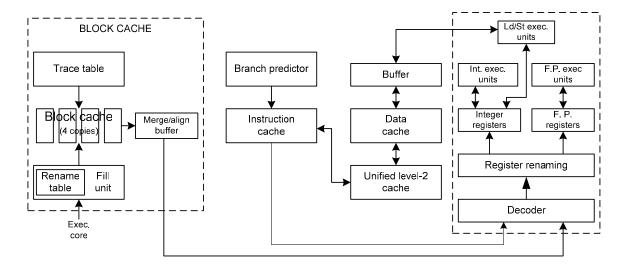

| 10   | A superscalar processor with a block cache (BC)                                                                                                                                                                                                                                                                                                                                        | 21  |

| 11   | Basic blocks in block cache (BC): 3 blocks are fetched per cycle; each block is up to 6 instructions long. As compared to TC, there is a potential increase in block fragmentation, as well as in more 'instruction holes' being left in block cache lines. (Block execution sequence is the same as the examples of Figure 7 and Figure 9, but has been omitted here for clarity).    | 22  |

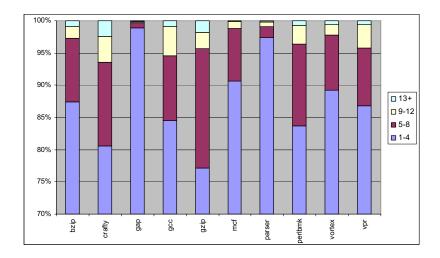

| 12   | Block length distribution in different SPECint2000 benchmarks                                                                                                                                                                                                                                                                                                                          | 27  |

| 13   | A superscalar processor with code pattern cache (CPC)                                                                                                                                                                                                                                                                                                                                  | 33  |

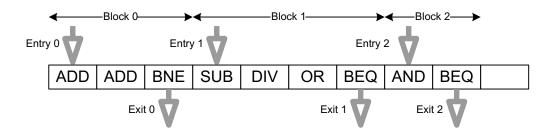

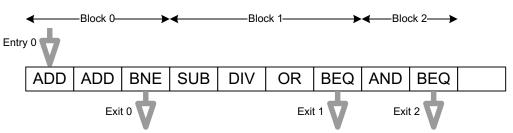

| 14   | CPC's "multiple-entry, multiple-exit" nature: A hit to a CPC trace is possible for any of three basic blocks (Block 0, Block 1, and Block 2). So, the trace line in this example has three entry points, Entry 0, Entry 1, and Entry 2. An exit happens when any of three blocks has a mispredicted branch at its tail. Possible exit points are marked as Exit 0, Exit 1, and Exit 2. | d   |

| 15   | TC's "single-entry, multiple-exit" nature: A hit to a TC trace is possible only when the trace starting address (meaning Block 0's head address) matches. So, the trace line in this example has only one entry point, Entry 0. An exit happens when any of three blocks has a mispredicted branch at its tail. Possible exit points are marked as Exit 0, Exit 1, and Exit 2.         | 36  |

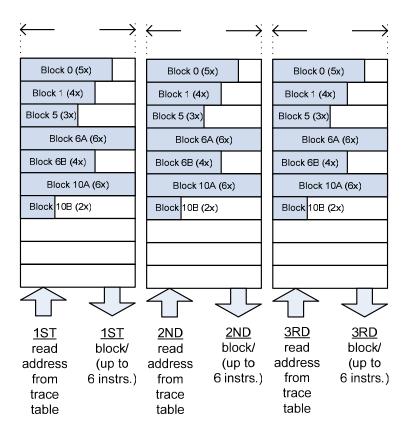

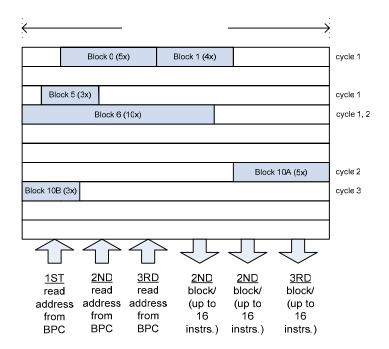

| 16   | Basic blocks in CPC's BBC structure: up to 3 blocks can be fetched per cycle. The ability to store and fetch variable block lengths can make a CPC-trace exceed TC and                                                                                                                                                                                                                 | 27  |

|      | BC-traces in size                                                                                                                                                                                                                                                                                                                                                                      | 37  |

| 17   | Overall view of the CPC-ST architecture                                                                                                                                                                                                                                                                                                                                                | 38  |

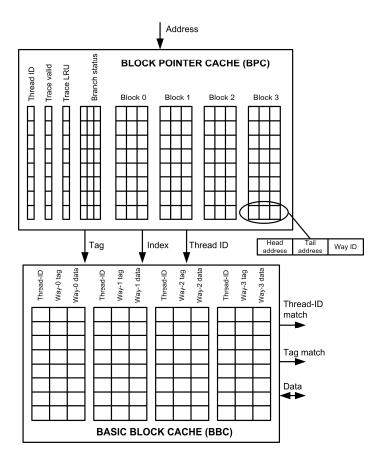

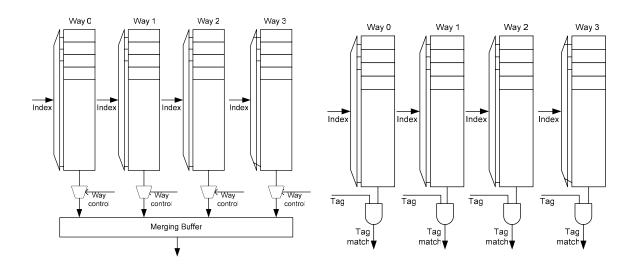

| 18   | BPC-BBC interconnection                                                                                                                                                                                                                                                                                                                                                                | 39  |

| FIGURI |

|--------|

|--------|

| Page |

|------|

|------|

| 19 | BPC trace line: The line includes block head and tail addresses, and the ID's of BBC-ways where basic blocks are stored.  Other fields include thread-ID, branch status, and LRU bits | 40 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 20 | BBC Data Array: The array stores the basic blocks of varying lengths.                                                                                                                 | 41 |

| 21 | BBC Tag Array: Tag matching is done to determine presence of basic blocks in a BBC-way                                                                                                | 41 |

| 22 | Trace build buffer: The buffer entry is completed upon detection of end of block condition and after the block-end branch status is known.                                            | 42 |

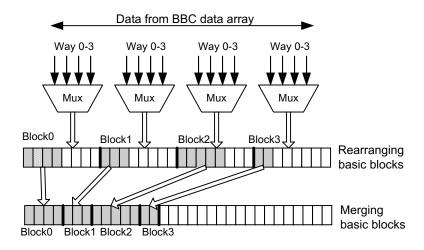

| 23 | Merging buffer: Blocks retrieved from different BBC-ways are first re-arranged (in execution order) and aligned before being sent for execution                                       |    |

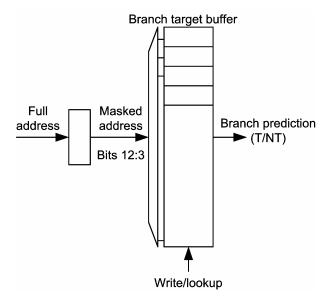

| 24 | Branch predictor implemented in the form of a branch history table.                                                                                                                   | 44 |

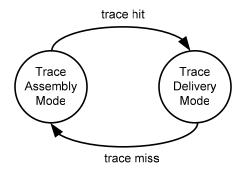

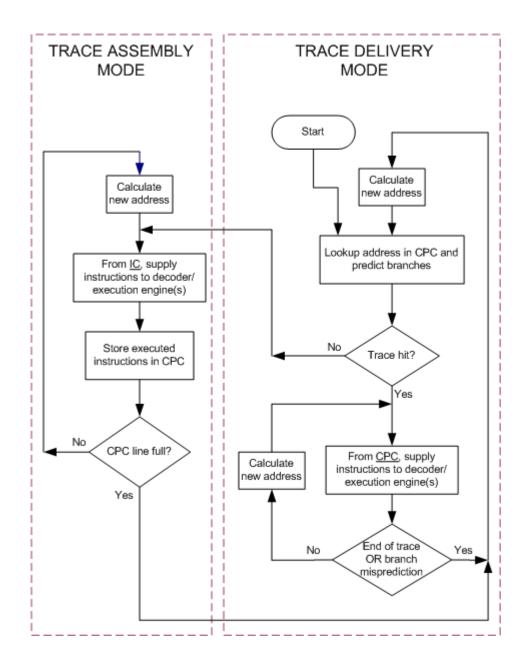

| 25 | CPC's two modes of operation: trace assembly mode and trace delivery mode                                                                                                             | 45 |

| 26 | A high-level view of the functions performed by CPC: Tasks specific to the two operating modes are enclosed in the larger outer boxes.                                                | 47 |

| 27 | Information for a single trace that has four basic blocks of different lengths                                                                                                        | 51 |

| 28 | A BPC line that contains trace information for the trace in Figure 27. Only the first BPC line contains a valid trace                                                                 | 52 |

| 29 | Placement of 4 basic blocks for a single trace in BBC: 2 basic blocks are in the same way while other two basic blocks land in their own BBC-ways.                                    | 52 |

| 30 | Three valid traces in BPC: There is one basic block (highlighted) that appears twice in the first trace and again in the 3 <sup>rd</sup> trace.                                       | 53 |

| FIGU | RE P                                                                                                                                                                                                                                                                                                            | age     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31   | BPC LRU after n, n+1, and n+2 hits on BPC-line 2                                                                                                                                                                                                                                                                | 54      |

| 32   | BBC LRU fields are 3 bits wide. Each way has its own set of LRU bits (Tag and data fields are not shown for clarity)                                                                                                                                                                                            | 55      |

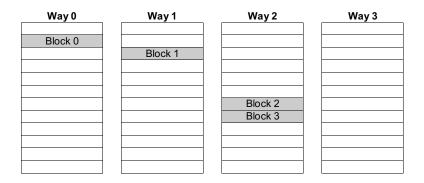

| 33   | Changes in BBC LRU values after 3 hits to the same BBC-way                                                                                                                                                                                                                                                      | 56      |

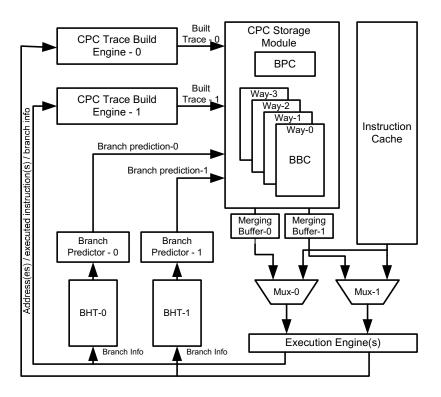

| 34   | Examples of BBC addressing fields: Tag and index information for 3 blocks is shown.                                                                                                                                                                                                                             | 58      |

| 35   | Block placement in BBC: The index values of Figure 34 determine block locations in BBC. Way-selection is done using the LRU bits (not shown)                                                                                                                                                                    | 59      |

| 36   | Overall view of a CPC-MT-based system                                                                                                                                                                                                                                                                           | 60      |

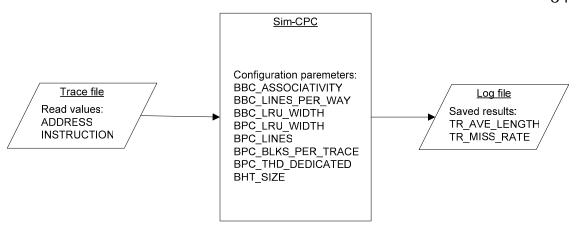

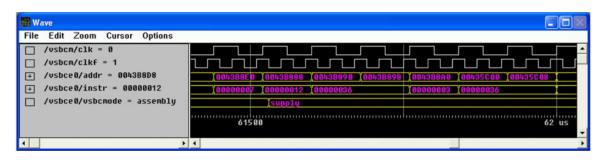

| 37   | Sim-CPC simulator with inputs and outputs: A single set of inputs (address and instruction) is read from the trace file every cycle. At the end of the simulation, the outputs (trace miss rate and average trace length) are saved in a log file. Sim-TC and Sim-BC operate on the same principles as Sim-CPC. | 64      |

| 38   | Sim-CPC simulation using ModelSim: An address ( <i>addr</i> ) and an instruction ( <i>instr</i> ) are read from the benchmark trace file ever <i>clk</i> cyle. A trace hit causes operation-mode switch from <i>trace</i> assembly to <i>trace delivery</i> (supply) at 61530 ns                                | ry      |

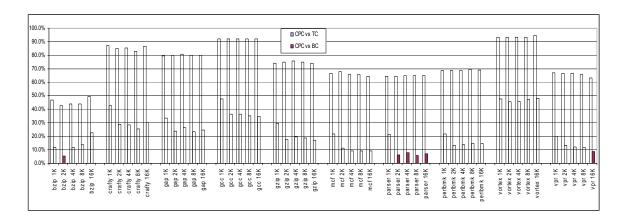

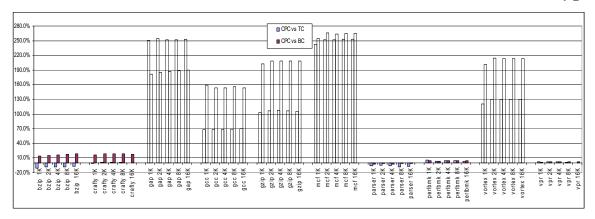

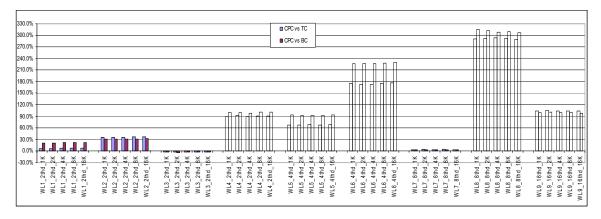

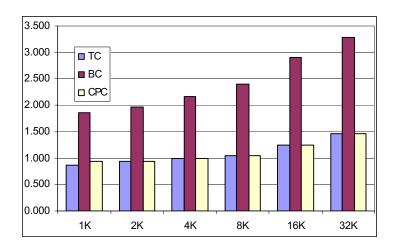

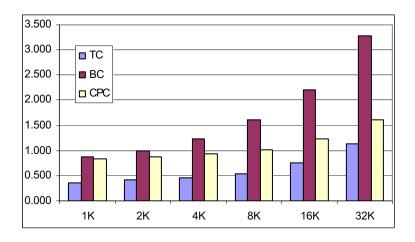

| 39   | CPC's miss rate comparison with TC and BC in single-threading environment. On average, CPC is 73.7% better than TC and 22.7% better than BC.                                                                                                                                                                    | g<br>69 |

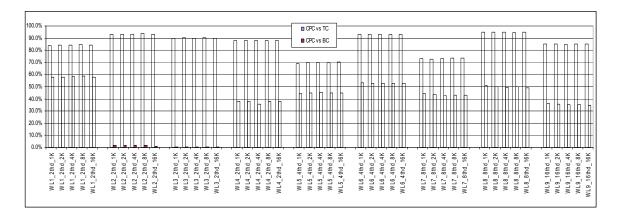

| 40   | CPC's miss rate comparison with TC and BC in multi-threading environment. On average, CPC is 85.7% better than TC and 36% better than BC.                                                                                                                                                                       | 70      |

| 41   | CPC's trace length comparison with TC and BC in single-threading environment. On average, CPC is 79.7% better than TC and 106.1% better than BC                                                                                                                                                                 | 71      |

| 42   | CPC's trace length rate comparison with TC and BC in multi-<br>threading environment. On average, CPC is 86.1% better<br>than TC and 98.4% better than BC                                                                                                                                                       | 72      |

FIGURE Page

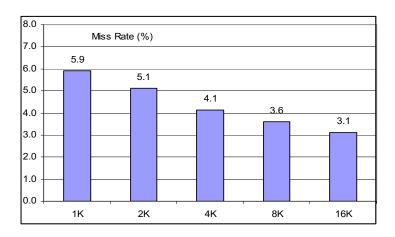

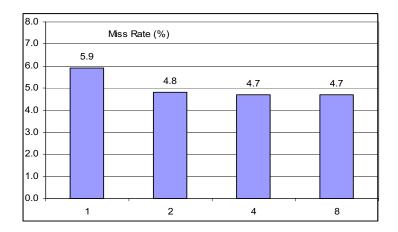

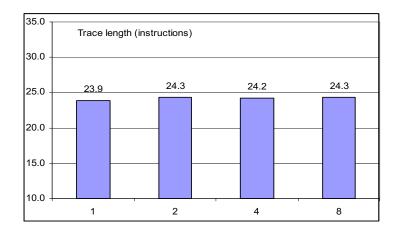

| 43 | Effect of varying CPC cache (BPC) size (shown on horizontal axis) on miss rate: A drop in miss rate happens with increase in BPC capacity.                                                    | 73 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

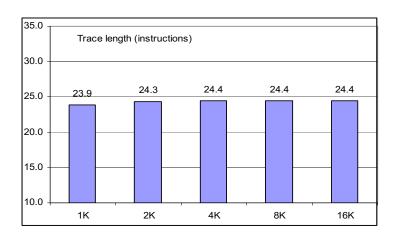

| 44 | Effect of varying CPC cache (BPC) size (shown on horizontal axis) on trace length. The trace length is relatively insensitive to cache size.                                                  | 74 |

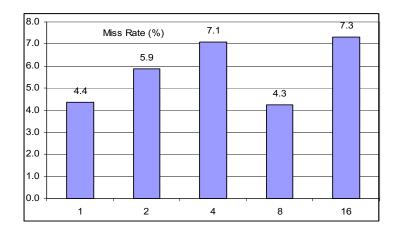

| 45 | Effect of varying CPC-BBC associativity on miss rate: After an initial drop in miss rate, it flattens out with increase in associativity. (Horizontal axis shows number of BBC-ways.)         | 75 |

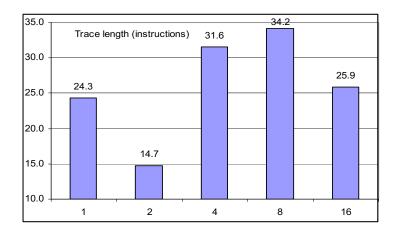

| 46 | Effect of varying CPC-BBC associativity of trace length: The trace lengths are not affected very noticeably with the change in BBC-associativity. (Horizontal axis shows number of BBC-ways.) | 76 |

| 47 | Effect of varying thread count on miss rate: Miss rates do not seem to have a consistent correlation with the thread count. (Horizontal axis represents thread-count.)                        | 77 |

| 48 | Effect of varying thread count on trace length: No clear relationship between thread count and trace lengths is visible. (Horizontal axis represents thread-count.)                           | 77 |

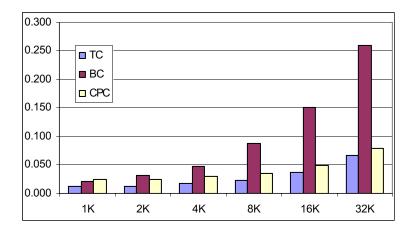

| 49 | Access time (ns) comparison for TC, BC, and CPC                                                                                                                                               | 81 |

| 50 | Power comparison (nJ) for TC, BC, and CPC                                                                                                                                                     | 82 |

| 51 | Area comparison (cm^2) for TC, BC, and CPC                                                                                                                                                    | 83 |

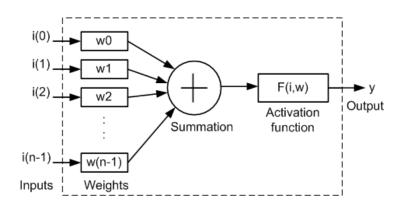

| 52 | Processing element – building block of a neural network                                                                                                                                       | 87 |

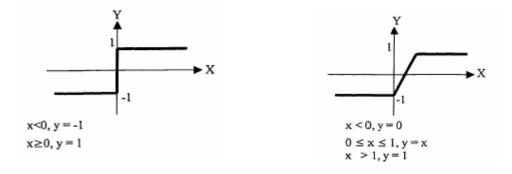

| 53 | A step activation function                                                                                                                                                                    | 88 |

| 54 | A ramp activation function                                                                                                                                                                    | 88 |

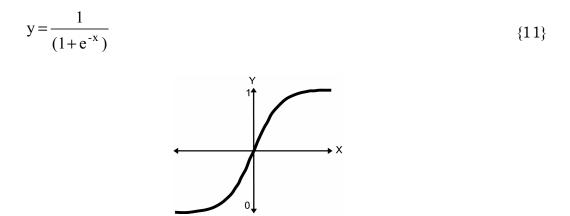

| 55 | A sigmoid activation function                                                                                                                                                                 | 88 |

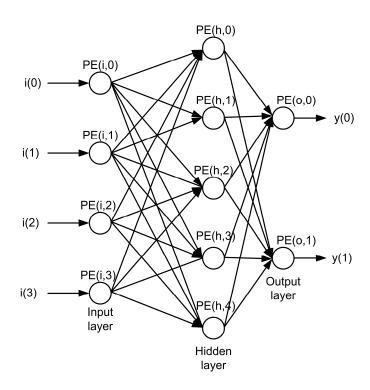

| 56 | Topology of a 3-Layer Feed-Forward Neural Network                                                                                                                                             | 89 |

| FIGU | RE                                                                                                                                                                                                                                                                                           | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

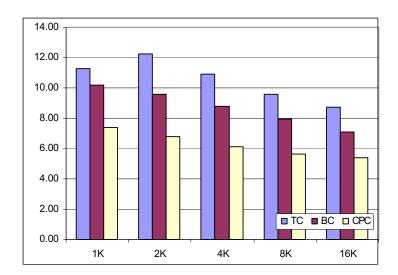

| 57   | For a program with arbitrarily chosen 'block size distribution' {0.80, 0.17, 0.03, 0.02}, miss-rate NNM was used to predict the values for TC, BC, and CPC. The horizontal axis shows cache size in KB and the vertical axis represents miss rate percentages.                               |      |

| 58   | For a program with arbitrary chosen 'block size distribution' {0.80, 0.17, 0.03, 0.02}, trace-length NNM was used to predict the values for TC, BC, and CPC. The horizontal axis shows cache size in KB and the vertical axis represents the trace length in terms of number of instructions |      |

#### CHAPTER I

#### INTRODUCTION

Stated simply, the steps in a program execution are: (1) fetching an instruction; (2) reading the related data; (3) performing calculations; (4) and storing the results (to memory or register file, if needed); then going back to the 1st step to fetch the next instruction [Hennessy & Patterson 2003]. In order to perform these tasks, a modern processor can be organized as a structure that is divided into an instruction fetch unit (called producer) and an instruction execution unit (called consumer). The producer and the consumer are separated by instruction issue buffers (collectively called the instruction window). The goal is that the producer issues the instructions at the highest possible rate while the consumer attempts to execute the instructions as fast as it can [Hennessy & Patterson 2003]. With the ongoing validity of nearly 40-year old Moore's Law [Moore 1965], an ever-increasing number of devices are available to the processor designers, who are faced with the constant challenge of balancing the performance, design complexity, testability, manufacturability, and all the related costs.

In this dissertation, we present a new method of improving producer performance by introducing a new instruction cache, called code pattern cache (CPC). CPC's functionality is based on the execution patterns (dynamic nature) of programs. In plain terms, CPC's salient features are:

- It exploits the empirical observation that a program's sets of instructions (blocks) come in varying sizes

- It does not require that the same set of instructions be stored in multiple locations

- It does not need to replicate the cache structures

- It makes use of the (traditional) principle of cache associativity

- It increases the likelihood of finding previously executed sequences of instructions (*traces*) inside the cache, and every time it finds a sequence, CPC-traces tend to contain more instructions than existing schemes

- It maintains its ability to deliver traces even while serving multiple consumers

The other contribution of this dissertation is the creation of neural network models (NNM's) for CPC and similar cache schemes. The models can be used to perform what-if analyses of cache design space without running the time-consuming simulations.

CPC's performance measures are:

- The likelihood of finding instructions (*hits*) in cache

- The number of instructions found with each hit

- The die area it takes to implement the cache

- The power consumed by the cache

- The time it takes to access the cache

This chapter first broadly covers the aspects of microprocessor performance and different approaches for its improvement, and then discusses the motivation and contributions of this dissertation in detail.

#### 1.1 Background

#### 1.1.1 Microprocessor Performance

In order to speed up program execution, one may simply use larger or faster semiconductor circuits that make use of newer and smaller transistors. One use of increased availability of transistors is to increase the number of instruction execution units. The number of execution units determines the maximum number of instructions that can be issued by the *producer* in one processor clock cycle [Hennessy & Patterson 2003]. A processor with multiple execution units is called a *superscalar* processor. Using a larger number of execution units results in increased die size and power consumption, which may not be desirable for cost-effective designs. Besides utilizing faster circuits,

today's high-performance processors use many techniques, such as caching and branch prediction; these two techniques make use of the pragmatic behavior of the programs, which assume that their execution behavior is not random, and that it follows certain patterns. The branch prediction helps fetch instructions from memory (and sometimes even execute them) in advance without knowing the outcome of the current instruction [Hennessy & Patterson 2003]. In other words, branch prediction exploits the regularity in the program flow. Caching operation is based on the observation that the programs tend to access contiguous locations in memory (spatial locality) or the recently accessed memory locations repetitively (temporal locality) [Hennessy & Patterson 2003]. This program behavior results in low latency (how fast the memory contents are available) and higher bandwidth (how much data is readily available) for caches. Effectively, the caches try to approximate the availability of ideally large memory that the programmers expect [Hennessy & Patterson 2003]. Another reason why the memory latency is critical is that the processor speed has risen at a rate much higher than memory speed. This increasing gap is a constant challenge for processor system designers. The issue is particularly significant for applications that require large memory bandwidth, such as digital image-processing, especially if the data needs to be transferred over a simple, standard interface. So the issue of memory latency becomes ever more important [McBader & Lee 2003].

One or more levels of caches can be used between the processor and the main memory; placing fast caches close to the processor reduces memory latency by storing frequently or recently accessed data and instructions. The caches closest to the processor are fast but small in size, whereas longer latency caches are larger in size and store less frequently accessed data and instructions [Shanley & Anderson 1995].

The caches go only so far with the alleviation of memory latency constraints because of cache misses and the resulting processor stalls. So it becomes imperative to manage the caches efficiently. Two important aspects of cache management are: (1) when and how much data to bring into cache (*pre-fetching*); and (2) what to retain in cache and what to replace [Hennessy & Patterson 2003].

#### 1.1.2 Overview of Thread-Level Parallelism

Kavi et al. (1995) define a *thread* as a set of instructions that starts execution at its first instruction and continues execution without interruption. A single program can be executed on multiple processors that have shared code and (most of the) address space. Sharing of code and data in this manner is traditionally called *threading*. These days, threading also refers to execution in multiple locations even when the

address space is not shared [Hennessy & Patterson 2003]. A programmer can identify independent threads or he can use a compiler for this purpose. Threads can be large, fully independent programs or parts of a single program (for example, parallel iterations in a loop). Parallelism is defined as the potential of simultaneous execution and thread-level parallelism (TLP) is "logically structured as separate threads of execution." The exploitation of thread-level parallelism is an effective way of overcoming the limitations of memory latency [Hennessy & Patterson 2003]. Instruction level parallelism (ILP), in contrast, exploits the ability to multiple instructions issue in а cycle. In hardware-related implementation, opportunities for ILP are identified and scheduled by hardware; whereas, software-centric ILP depends on static scheduling by a (very long instruction word) compiler. ILP's main advantage is that it makes use of parallelism without requiring re-writing of the existing programs [Schlansker et al. 1997].

Multi-threading (MT) is a technique that allows multiple threads to share the execution units of a single processor in a parallel fashion. The hardware must support the switching of threads efficiently. To enable MT, some components of a processor (for example, the register file and the program counter) need to be replicated. Sharing of memory can be done via the *virtual memory* technique [Hennessy & Patterson 2003].

(Virtual memory (VM) automates the job of moving program and data between the main memory and secondary storage. One of VM's advantages is the ease for a programmer, especially, when his program code and data sizes exceed the physically available memory [Jacob & Mudge 1998]).

Fine-grain MT and coarse-grain MT are two main approaches to MT. Fine-grain MT allows switching of threads on every instruction, in a round-robin fashion (while skipping any stalled threads). On the other hand, coarse-grain MT switches threads when the currently executing thread stalls for many cycles due to for example, a miss on the cache closest to the main memory [Hennessy & Patterson 2003].

Figure 1 shows the states of 4 execution units (EU1-EU4) of a (single-threaded) superscalar processor in several cycles. Different executions units are used every cycle for the same thread T1. A *used* execution unit is represented by a box containing letter T followed by the thread number; an *unused* execution is shown as an empty box (Figure 2, Figure 3, and Figure 4 also follow the same conventions). In Figure 1, we see that in cycle n, EU1 and EU2 are used, while EU3 and EU4 remain unused; in cycle n+1, EU2 and EU3 are used, while EU1 and EU4 remain unused; and so on. Due to a stall on T1 during cycle n+4, all four execution units remain unused.

Figure 1. States of 4 execution units of a superscalar processor executing a single thread (T1)

The states of execution units in a fine-grain MT processor are shown in Figure 2.

Figure 2. States of 4 execution units of a fine-grain MT processor executing 3 threads (T1, T2, T3); threads switch in roundrobin fashion every cycle.

Three threads T1, T2, T3 get executed on the processor. In cycle n, two executions EU1 and EU2 are used by thread T1; in the next cycle n+1, T2 uses the same execution units; and so on. This threadswitching continues in a round-robin fashion, unless some thread is

skipped due to a stall; this happens in cycle n+5, where T2 is passed over by T3.

Figure 3. States of 4 execution units of coarse-grain MT processor executing two threads (T1 and T2); thread switches from T1 to T2 in cycle n+3 due to long stall on thread T1.

The coarse-grained MT does not switch from the currently running thread to the next unless there is a long (multi-cycle) stall on the current thread. For example, in Figure 3, thread T1 keeps occupying different execution units during n, n+1, and n+2 cycles, until a stall on T1 causes T2 to start executing in cycle n+3.

In the case of simultaneous multi-threading (SMT), TLP and ILP techniques are combined concurrently [Hennessy & Patterson 2003]. SMT allows multiple issues of independent threads to multiple execution units per cycle [Tullsen et al. 1995]. Processor resources in an SMT processor are shared among threads on per-cycle basis. But, as the processor has to hold instructions from multiple threads, larger issue

instruction queues may be required [El-Moursy & Albonesi 2003]. (Instructions are held in an instruction queue before being sent to execution units). The term Hyper-Threading is used for the implementation of dual-thread SMT on Intel's Pentium-4 and Xeon processors [Intel 1997], [Intel 2001], [Marr 2002]. The SMT processor of Figure 4 shows that during a given cycle, more than one thread is allowed to execute. For example, T1 and T2 execute simultaneously in cycle n, T1 and T3 execute in cycle n+1, and so on. The result can be better utilization of execution ('consumer') resources.

Figure 4. States of 4 execution units of a simultaneous multithreading (SMT) processor. Based on the availability of execution units, instructions from one or more threads are allowed to execute every cycle.

An MT processor alters the way the memory is accessed. Cache effectiveness is reduced because of the changed locality of reference [Lioupis & Milios 1997]. To address this issue, an MT architecture presented by Govindarajan et al. (1995) had separate instruction and

data caches. Lioupis & Milios (1997) studied behavior of a single-thread in an MT processor with different cache configurations. They proposed a pipelined interface between the cache and the rest of the memory hierarchy for better cache performance.

#### 1.1.3 Basic Blocks

A basic block is a set of contiguous instructions that contains only a single control instruction such as a conditional or an unconditional jump, a return, or a call. The control instruction is the last instruction of a basic block, and is also called the block tail. The beginning of a basic block is called its block head. Block head is also the destination of a control transfer instruction [Ozturk et al. 2005]. In this dissertation, basic blocks have no size limitations other than the cache capacity.

| Address | Instruction | Comments                                                       |

|---------|-------------|----------------------------------------------------------------|

| 0000    | ADD         | Block 0 head on the 1 <sup>st</sup> instruction of the program |

| 8000    | ADD         |                                                                |

| 0010    | BNE         | Block 0 tail due to a conditional jump                         |

|         | :           |                                                                |

|         | :           |                                                                |

| 0030    | ADD         | Block <i>m</i> head                                            |

| 0038    | SUB         |                                                                |

| 0040    | ADD         |                                                                |

| 0048    | DIV         |                                                                |

| 0050    | J           | Block <i>m</i> tail due to an unconditional jump               |

|         | :           |                                                                |

|         | :           |                                                                |

| 0058    | ADD         | Block n head                                                   |

| 0060    | MULT        |                                                                |

| 0068    | OR          |                                                                |

| 0070    | ADD         |                                                                |

| 0078    | BEQ         | Block n tail due to a conditional jump                         |

|         |             |                                                                |

| 1000    | SUB         | Block x head                                                   |

| 1008    | HLT         | Block x tail; halt instruction terminates the program          |

Figure 5. Four basic blocks from a sample program are shown. Block beginnings (heads) and (tails) are also identified. (Addresses are shown in hexadecimal format).

A sample assembly program with some control instructions is shown in Figure 5. The program contains conditional and unconditional jumps. The beginning and the end of each block is also indicated. The code in this example shows four basic blocks. Basic block 0 starts with the 1<sup>st</sup> instruction of the program and ends with a conditional branch (BNE). The *head* address of this block is 0000 and the *tail* address is 0010. The length of this block is 3 instructions. The *head* of block *m* at address 0030 is the destination of a conditional or unconditional jump from (the same or a different) basic block. The *tail* of this block at address

0050 is determined by an unconditional jump instruction (J). The length of this block is 5 instructions. Similarly, block *n* has its *head* and *tail* at addresses 0058 and 0078, respectively. The last block *x* starts at address 1000; the block ends with a halt (HLT) instruction at address 1008.

#### 1.1.4 Conventional Instruction Cache

The basic data unit of conventional instruction cache (IC) is a cache line that stores a set of memory-adjacent instructions. The usual cache line lengths are 16 to 64 bytes. IC, although simple to implement, tends to exhibit high latency and low bandwidth. Typically single-ported reads limit IC bandwidth to a single basic block because of a jump to a non-adjacent memory location. This type of jump is called a takenbranch. A simplified block diagram of a superscalar processor with an IC is shown in Figure 6 [Hennessy & Patterson 2003]. The instructions are provided from the IC to the decoder. Only one cache line can be delivered per cycle. The basic blocks beyond a taken-branch are fetched in the following cycle as illustrated by block #5 in cycle 2 in Figure 7. (In Figure 7, Figure 9, and Figure 11, a number before an 'x' represents the instruction count in a basic block. The upper case 'A' or 'B' used as a suffix to a block number indicates that the block is split over two cache lines. The arrows indicate the instruction flow.)

Figure 6: A superscalar processor with an instruction cache (IC)

Assuming that no pre-fetch buffer is present, the example in Figure 7 requires 5 cycles to fetch the two contiguous blocks (#0, #1) and three non-contiguous blocks (#5, #6, #10). Note that block #10 straddles across 2 cache lines. So the fetching of this block is split over two cycles.

Figure 7. Basic blocks in the lines of an IC: 5 cycles are required to fetch the non-contiguous basic blocks due to taken branches. (The arrows show the sequence of instruction execution).

Much research has been done on techniques that improve bandwidth beyond IC. For example, Dutta & Franklin (1995) (1999) used a tree-like subgraph for an executed program to predict multiple branches in a single prediction. Hao, et al's (1996) block-based architecture depended on compile-time and hardware-based solutions. However, they introduced redundancy in storage when they combined basic blocks to create larger blocks.

As mentioned earlier, branches can make a program jump out of a cache line. When *taken*, the branches in the middle of a cache line leave many unexecuted instructions and hence cost additional read cycles to

fetch another line. (A taken-branch usually jumps to a non-contiguous program location). Keeping this IC behavior in view, techniques for improved instruction fetching have been presented by Conte et al. (1995), Hily & Seznec (1996), McFarling (1993), Wallace & Bagherzadeh (1998), and Yeh & Patt (1992). Conte et al's (1995) collapsing buffer scheme was able to align non-adjacent basic blocks up to 90% of the time. McFarling (1993) combined different branch predictors in such a way that only the most accurate prediction was used for a branch. Hily & Seznec's (1996) study on three common branch predictors included use of branch history tables whose sizes proportionally increased with the number of programs executing in parallel. Wallace & Bagherzadeh's (1998) instruction fetch mechanism involved a dual branch target buffer that tried to predict the starting addresses of the next two cache lines. Yeh & Patt's (1992) adaptive branch prediction scheme used two levels of branch prediction by looking at the n-level history of the last few branches. All of these techniques still limited the instructions fetched per cycle to one or two basic blocks. For better performance, more basic blocks need to be fetched every cycle which is possible in Rotenberg et al's (1999) trace cache (TC) and other follow-up schemes [Black et al. 1999], [Jourdan et al. 2000].

#### 1.2 Related Works

#### 1.2.1 Trace Cache

Rotenberg, et al's (1999) TC bypassed IC's fundamental instruction limit due to taken branches and resulted in increased bandwidth and reduced latency of instruction decoding. TC also addressed some of the issues present in the previous schemes (refer to previous section) [Conte et al. 1995]. TC captured instructions as they were executed. The matching of the starting address of a TC line and the predictions for branches inside the line are the two conditions that cause the delivery of instructions (to the instruction decoder) from TC, instead of IC. TC made it possible to fetch multiple basic blocks in one cycle (Refer to Figure 9) [Black et al. 1999], [Gummaraju & Franklin 2000], [Howard & Lipasti 1999], [Jourdan et al. 2000], [Patel et al. 1998], [Patel et al. 1999].

Figure 8. A superscalar processor with a trace cache (TC)

The block diagram of a TC-based superscalar microarchitecture is shown in Figure 8. A single TC-trace may contain more than one block. When there is a TC-hit, more than one basic block can be delivered to the decoder in the same cycle. In case of a miss on TC, a cache line is brought from the IC.

Figure 9. Basic blocks in the lines of a trace cache (TC): A maximum of 16 instructions or 3 basic blocks are stored in a TC line. 'Instruction holes' are left at the end of the first cache line. In cycle-1, 3 basic blocks are delivered. (The arrows show the sequence of instruction execution).

In the TC in Figure 9, a cache line contains a maximum of 3 basic blocks or 16 instructions. Blocks #0, #1, and #5 are all fetched in one cycle. Three blocks in the first line have only 12 instructions, so space for three instructions is left unused. In other words, three 'instruction holes' are left at the end of the cache line. Although block #10 still happens to cross the cache line boundary, fetching of up to 16 instructions is now possible in cycle 2. In case of TC, only 3 (instead of 5)

cycles are needed to fetch the same set of instructions as the conventional IC (of Figure 7).

#### 1.2.2 Block Caches

A variation of TC was Black, et al's (1999) cache scheme called block cache (BC). The scheme included identification of individual blocks in the stored traces. The block identifiers (pointers) were used to assemble the traces, on a trace hit. In BC, two separate cache structures were used, one (called block cache) to store the basic blocks and the other (called trace table) to store the block pointers. The blocks were replicated 4 times in Black et al's (1999) scheme. Each line in the block cache stored a single basic block. The assumption that basic blocks were all the same width caused an increase in the likelihood of block fragmentation. (Refer to Figure 11 for the examples of fragmented blocks). Black et al. (1999) reported that, with perfect branch prediction, BC helped a processor complete 7% more instructions per cycle than TC. However, they did not compare BC's trace miss rate and average trace length with TC.

Figure 10. A superscalar processor with a block cache (BC)

The block diagram in Figure 10 shows a superscalar processor connected to BC. The trace table is used to determine a BC-hit or a miss. On a hit, the basic blocks are fetched from the block cache. A complete trace is built by passing instructions through the merge/align buffer being sent to the decoder. A BC-miss causes delivery of instructions from the IC.

Figure 11. Basic blocks in block cache (BC): 3 blocks are fetched per cycle; each block is up to 6 instructions long. As compared to TC, there is a potential increase in block fragmentation, as well as in more 'instruction holes' being left in block cache lines. (Block execution sequence is the same as the examples of Figure 7 and Figure 9, but has been omitted here for clarity).

In Figure 11, three blocks are fetched every cycle with each block containing a maximum of 6 instructions. All blocks that are longer than 6 instructions have to be split over more than one block cache line. When blocks are not multiples of 6 instructions, instruction holes are encountered at the end of block cache lines. In Figure 11, there are two fragmented blocks (#6 and #10) (vs. the TC of Figure 9 that has only one

such block, i.e., block #10). Also, one can observe the redundancy of storage; each basic block must be stored in 3 identical cache structures.

A scheme similar to BC was proposed in a Jourdan, et al. (2000). Their scheme, called *extended block* (XB) cache, stored the instructions (uops) in reverse sequence, giving them the ability to extend any existing XB's. They reported reduced block fragmentation. Black et al. (1999) and Jourdan et al. (2000) reported cache performance results only for single-threaded environments. The XB bandwidth was similar to TC. Due to this marginal improvement over TC and due to XB's significantly complex implementation logic, we will limit our discussion of XB to this section only and will not use XB for performance comparison in our research. Unlike TC, no follow-up research has been reported on either BC or XB, since their introduction.

## 1.2.3 Modeling Techniques

Simulation models provide a faster method of studying the design or operation of a system compared to actual implementation [Smith 1994]. Usually, *mathematical* or *analytical models* comprise a set of mathematical equations. NNM's, on the other hand, are made up of a set of weights that are applied to the model inputs to calculate the outputs. (Chapter IV discusses NNM's in detail). Mathematical models based on response curves (polynomial, spline, etc.) are ineffective with highly non-

linear systems, while NNM's excel with large number of parameters [Stegmayer & Chiotti 2004]. NNM's are robust and provide a good alternative to lookup methods that require storage of all data points in a given data space [Simpson et al. 1997].

In the past, mathematical models and NNM's have been used to model electronic systems and sub-systems. A few examples of mathematical or analytical models are: the model of a program behavior to predict the miss ratio of a fully-associative cache [Singh et al. 1992]; the model of a superscalar processor that included interaction of parallelisms in programs and machines as a performance measure [Noonburg & Shen's 1994); the model for instruction-fetch performance of superscalar processors [Wallace & Bagherzadeh 1998); the miss-ratio model for set associative caches [Harper, et al. 1999); and the model for TC [Hossain et al. 2002). Examples of NNM's are: the NN-based controller to adjust the memory resources in a multi-programming system [Bigus 1994]; the model for analog component behavior [Sobecks et al. 1998]; and the analysis tool that finds bottlenecks in a computer system, such as memory, network, processor, etc. [Gruen & Kubota 2002].

Only in recent years has some research been published dealing with NNM's application to the field of computer architecture. One such example is Jimenez & Lin's (2001) NN-based branch predictor; it does not

suffer from the drawbacks of a conventional branch predictor whose hardware requirements rise exponentially when the branch histories are lengthened. The other example is an NNM for a cache replacement scheme presented by Khalid (1996), and Khalid & Obaidat (2000). The authors used an NNM for predicting the pattern of memory references made by the processor.

The effectiveness with which the NNM's usually model the nonlinear and multi-variate systems and the ease of NNM creation are the primary reasons for their use for cache modeling in this dissertation.

CACTI is an analytical model for estimating the area, power, and timing for caches [Wilton & Jouppi 1996]. Since its introduction, CACTI has been used as an estimation tool by several researchers. For example, Batson & Vijaykumar (2001) used this tool to estimate the hit-time for reactive-associative cache; the cache scheme implemented flexible associativity by placing most blocks in direct-mapped positions and reactively displacing only conflicting blocks to set-associative positions. Banakar et al. (2002) used CACTI to compute area and energy for their proposed scratch pad memory, an alternative to cache. Sangireddy et al. (2004) used CACTI to study a low-power technique for cache-based reconfigurable architecture. In our research, we use CACTI to compare

the area, power, and timing requirements for cache structures in TC, BC, and CPC.

#### 1.3 Motivation

Below, we have identified several issues with the current tracebased schemes, namely, TC and BC:

- There is a tendency for TC to have the same set of instructions (full or partial basic blocks) appear in multiple traces. A few examples of percentages of instructions overlapping among traces (for the SPEC2000int [Spec 2000] benchmark programs) are: crafty = 25.1%, mcf = 38.5%, bzip = 79.5%. Redundancy of traces between IC and TC was addressed by Ramirez et al's (2000) scheme, but redundancy of instructions stored in the TC itself was not considered. If the storage redundancy is removed, the cache could be used to store more traces, and hence the miss rate could be reduced.

- TC uses only the beginning address of a trace for matching. Blocks other than the beginning block are not identifiable, so even if the required instructions are present in the trace, the trace is declared a 'miss' and a new trace build is initiated. This rebuilding requires

المنارة للاستشارات

<sup>&</sup>lt;sup>1</sup> The traces were extracted from a TC built by modifying *sim-cache* (of SimpleScalar 3.0 tool suite) [Burger 1997], [Burger & Austin 1997]. TC size was fixed at 64 traces while each trace had a maximum of 16 instructions or 4 basic blocks. The benchmark programs [Spec 2000] were run for 200 million instructions.

unnecessary switching from *trace utilization* mode to *build mode*. (In trace utilization mode, the instructions are delivered from TC; and in the build mode, the instructions fetched from the IC are executed and the traces are built/stored in TC). If this mode-switching is reduced, the average number of instructions fetched per cycle can be improved.

• TC traces can leave unused spaces at the end of cache lines if a program (or part of a program) is made up of smaller basic blocks.

Cache space can be more efficiently used if the stored traces are of variable, rather than fixed lengths (as in BC), and if the trace lengths can exceed the usual limit of a cache line width.

Figure 12. Block length distribution in different SPECint2000 benchmarks

- BC scheme suffers block fragmentation because the basic blocks are assumed to be of fixed length. With the blocks sizes (4-6 instructions per block) assumed in TC/BC designs, some instruction fetch capability may remain under-utilized because, as we can see in Figure 12, up to 23% of the blocks contain more than 4 instructions, and up to 11% of the blocks contain more than 6 instructions. For example, *bzip* has nearly 13% of the blocks longer than 4 instructions, and *crafty* has 19% such blocks. Figure 12 shows the percentage values of block sizes and counts for different SPECint2000 benchmark runs.

- BC potentially has more block-level fragmentation with smaller block sizes (of 4 or so instructions). The fragmentation also happens when a *logical* basic block that is wider than the block cache width is split into more than one *physical* block [Black et al. 1999]. (Refer to the example of Figure 11).

- BC requires storage of same basic blocks in multiple places. Black,

et al's (1999) research has BC replicating the blocks 4 times.

Redundancy of cache structures, if removed, could reduce the die area and the consumed power.

### 1.4 Contributions

In this research, we focus on the implementation of new instruction cache architecture that improves the fetch rates beyond what existing trace-based caches have reportedly attained. The following are the salient contributions of this dissertation:

- (1) We introduce a new instruction cache scheme called *code pattern cache* (CPC); some of the current trace-based instruction issues that CPC addresses are: (a) eliminating TC's redundancy of instruction storage; (b) removing BC's duplication of caches (thus reducing consumed power and die area); (c) including way-associativity instead of BC's single-way structures; (d) resolving the issue of BC's block fragmentation; (e) allowing the traces to be of variable length; and (f) improving access time (over BC) by enabling simultaneous access to basic blocks and their pointers.

- (2) We have developed functional simulators for existing trace-based schemes (TC and BC) and CPC, operating in single-threaded mode.

The simulators were developed in VHDL and provided a means to compare the performance of different caches.

- (3) We have enabled multi-threaded operation on the VHDL-based simulators for TC, BC, and CPC. The simulators allow instantiation of any number of threads; the only limitation may be the ability of

- a simulation platform (VHDL simulator) to complete simulations in a reasonable amount of time.

- (4) We have studied the implementation aspects of TC, BC, and CPC, such as power, area, and access time. Comparisons were made for different cache capacities.

- (5) We propose an aggregate performance index that combines the simulation results (trace miss rate, average trace length) and modeling results (power, area, access time). The index provides the means to compare the overall performance of TC, BC, and CPC.

- (6) We have developed two NNM's for modeling caches, one for predicting their miss rates, and the other for predicting average trace lengths. Each NNM collectively models the behavior of TC, BC, and CPC. The NNM's provide a method that is several orders-of-magnitude faster than simulation for exploring the design space of the three caches. (Until the time of this writing, no other such models for any cache scheme have been reported in the research publications).

# 1.5 Performance Evaluation

In order to compare TC and BC with CPC, we use several performance metrics. Two of the metrics are: *trace miss rate* and *average* trace length. These metrics are considered to be among the most

appropriate in the context of trace-based caches (TC, BC, etc.). Trace miss rate is the percentage of references when a requested trace was not found in the cache. A smaller value of trace miss rate represents a lower average latency for cache data fetching. Average trace length can be considered to be a measure of how efficiently the cache storage space is being utilized. The longer the traces, the larger the number of instructions fetchable per cycle.

We use only one level of cache in our functional simulators since the main focus of our research is the cache's own performance rather than that of a complete processor system. Simulating only the cache functionality also means that no direct method of calculating the processor-related *instructions completed per cycle* metric is available.

We study the trace miss rate and average trace length by using the instruction traces saved from runs for each of the ten SPECint2000 benchmarks [Spec 2000] on single-threaded cache simulators. The saved traces have a maximum length of 10 million instructions. Multi-threading workload mixes have been created using the traces from the same 10 benchmarks. (Details about the benchmarks and the simulator configurations are given later).

In addition to trace miss rate and average trace length, we used area, power, and access time, as the performance metrics for cache implementation. Calculation of these 3 parameters is done using a readily-available cache analytical model called CACTI [Shivakumar & Jouppi 2001].

To make an overall comparison of different cache schemes, an aggregate performance index that combines the simulation and modeling results has also been used.

# 1.6 Organization of this Dissertation

The rest of this dissertation is organized as follows: Chapter II covers the CPC architecture and operation. Chapter III contains CPC simulation and modeling, and CPC's performance comparison with TC and BC. Chapter IV explains the use of NNM's for modeling the behavior of CPC and other caches. Finally, Chapter V presents the conclusions and suggests areas for future research.

# CHAPTER II

# CODE PATTERN CACHE

### 2.1 CPC Overview

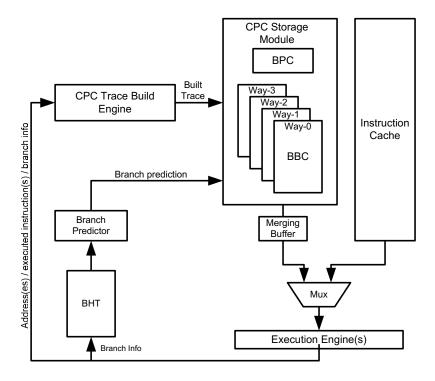

CPC stores sequences of instructions as they execute. When the same instruction sequence is encountered later, it is fetched from CPC instead of IC. Figure 13 shows the overall block diagram of CPC connected to a superscalar processor.

Figure 13. A superscalar processor with code pattern cache (CPC)

Unlike TC, the basic blocks that may appear in multiple traces are stored only once in CPC. The basic blocks are stored in basic block

cache (BBC), and the starting and ending addresses of the basic blocks are stored in a separate structure called block pointer cache (BPC). Each line in BPC represents a single trace by storing multiple sets of basic block (start and end) addresses. A merge-and-align buffer is used to 'assemble' a trace, before it is sent to the decoder and execution engine. The BPC lines also store the BBC way-number if BBC is configured as an n-way associative structure. Unlike BC, storage and retrieval of block sizes of varying lengths are allowed by CPC. Combined effects of variability of block sizes and set-associativity in BBC tend to lower the trace miss rate. CPC's average number of instructions stored per trace is generally higher than both TC and BC. Cache storage in CPC is more efficient than BC because the former needs replication of cache structures. TC uses only the beginning address for trace matching. Because blocks other than the beginning block are not identifiable, the trace is declared a 'miss' and a new trace build is initiated even if the required instructions are present in the trace. CPC avoids this unnecessary switching from trace utilization mode to build mode by allowing hits on intra-trace blocks; this helps improve the trace miss rate. Fixed-length BC lines may increase the chances of basic block fragmentation, i.e., the blocks straddling across multiple cache lines and leaving unused spaces at the end of the lines (instruction holes); CPC is

likely to have fewer instruction holes than TC. CPC's implementation in hardware is only slightly more complex than TC but is simpler than BC. Multiple branch predictions for end-of-block addresses are also required in a manner similar to TC and BC.

CPC is a "multiple-entry, multiple-exit" cache (Figure 14). This means that a CPC trace can start execution from any of its basic blocks instead of just the first one and exits can happen when a branch at the end of any basic block does not match the outcome of branch prediction.

Figure 14. CPC's "multiple-entry, multiple-exit" nature: A hit to a CPC trace is possible for any of three basic blocks (Block 0, Block 1, and Block 2). So, the trace line in this example has three entry points, Entry 0, Entry 1, and Entry 2. An exit happens when any of three blocks has a mispredicted branch at its tail. Possible exit points are marked as Exit 0, Exit 1, and Exit 2.

In comparison, TC is a "single-entry, multiple-exit" cache (Figure 15) [Rotenberg et al. 1999]. In TC, the execution of a trace always starts at the beginning instruction of a trace and can terminate on any of its intra-line branches.

Figure 15. TC's "single-entry, multiple-exit" nature: A hit to a TC trace is possible only when the trace starting address (meaning Block 0's head address) matches. So, the trace line in this example has only one entry point, Entry 0. An exit happens when any of three blocks has a mispredicted branch at its tail. Possible exit points are marked as Exit 0, Exit 1, and Exit 2.

In the example of Figure 16, up to three blocks can be fetched every cycle.

Figure 16. Basic blocks in CPC's BBC structure: up to 3 blocks can be fetched per cycle. The ability to store and fetch variable block lengths can make a CPC-trace exceed TC and BC-traces in size.

The blocks in a trace may contain a different number of instructions. The traces are allowed to exceed BBC line width. CPC is expected to have less block fragmentation than CPC.

The CPC architecture can be used both in single-threading and multi-threading modes. CPC's single-threaded version is called CPC-ST, and the multi-threaded version is called CPC-MT.

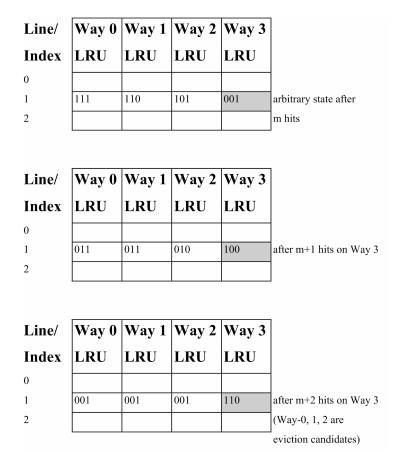

### 2.2 CPC-ST Architecture

An overall view of the CPC-ST architecture is shown in Figure 17.

Figure 17. Overall view of the CPC-ST architecture

The building blocks of this architecture are explained in detail in the following sections.